ADAHE:

Aceleración de análisis de Datos en Arquitecturas

Heterogéneas de alta eficiencia Energética

(Accelerating Data Analytics on Energy Efficient

Heterogeneous Architectures)

Aceleración de análisis de Datos en Arquitecturas

Heterogéneas de alta eficiencia Energética

(Accelerating Data Analytics on Energy Efficient

Heterogeneous Architectures)

Programa de ayudas a proyectos de I+D+i en el marco del Programa Operativo FEDER Andalucía 2014-2020 (Objetivo Específico 1.2.3. «Fomento y generación de conocimiento frontera y de conocimiento orientado a los retos de la sociedad, desarrollo de tecnologías emergentes»).

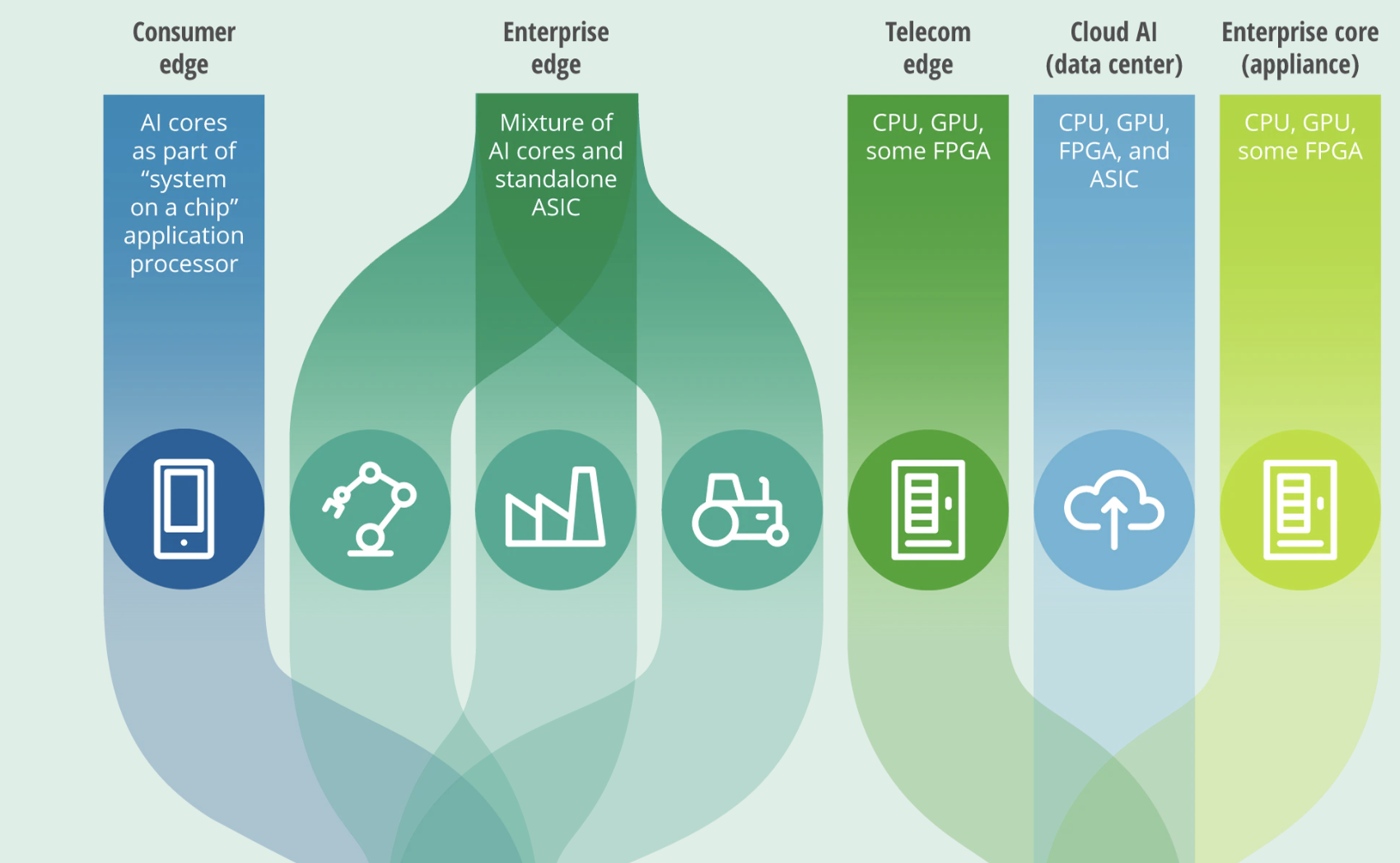

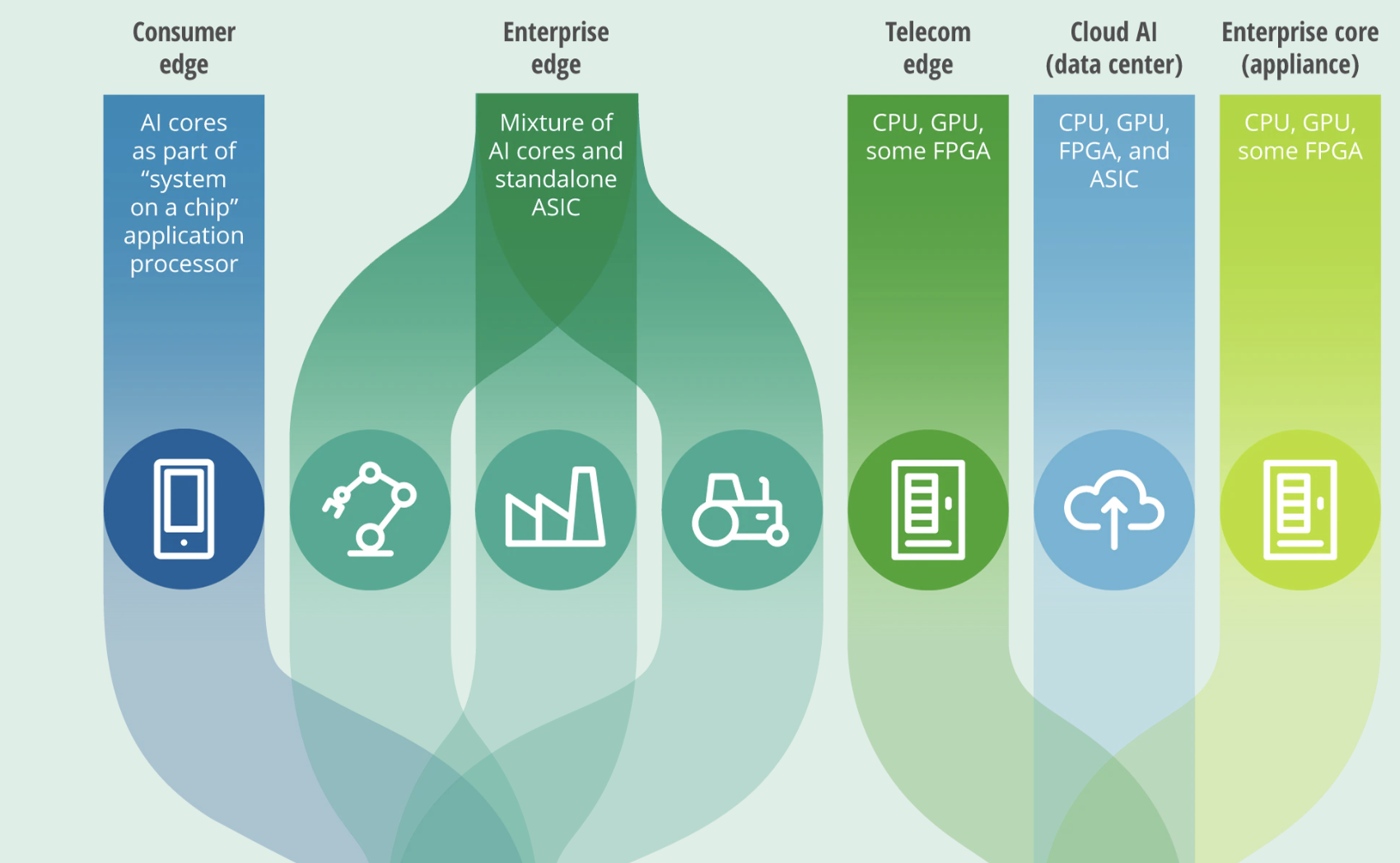

En este proyecto (ADAHE) pretendemos mejorar la productividad del programador de ciertas aplicaciones de alto impacto en arquitecturas heterogéneas con CPU+GPU+FPGA. Más precisamente nos centraremos en aplicaciones de análisis de datos masivos, principalmente en el campo de las series temporales (time series) y optimización matemática (mathematical programming). Se trata de aplicaciones utilizadas en dominios tales como economía, banca, predicciones financieras, bioinformática, sociología, logística, optimización de sistemas de producción y gestión de cadenas de suministro. Como caso de uso, utilizaremos aplicaciones de análisis de datos masivos aplicado al sector financiero y al sector energético que forman parte de los productos que desarrollan las micro-pymes que han demostrado interés en colaborar con ADAHE.

Nuestra visión es que se puede programar de forma productiva y reducir el coste de desarrollo y mantenimiento de este tipo de aplicaciones, así como reducir la factura energética (y por lo tanto el coste de explotación) en arquitecturas heterogéneas que incorporan aceleradores y que representan una nueva frontera en computación. Una importante dificultad en este tipo de aplicaciones se debe al hecho que muchas de ellas son de tipo irregular lo que significa que la mayoría de la computación suele estar organizada en torno a estructuras de datos dispersas (sparse), grafos, y muchas veces basadas en punteros, tales como árboles y listas de objetos. Además, en los dominios de interés de nuestras aplicaciones, la información se genera como un stream de datos que hay que procesar en tiempo real. Típicamente, los patrones de paralelismo que mejor pueden representar este tipo de aplicaciones irregulares son dataflow y branch and bound, patrones apenas estudiados en el contexto de arquitecturas heterogéneas paralelas.

Nuestra estrategia, basada en el co-diseño, está dirigida por el tipo de aplicaciones estudiadas: aplicaciones de análisis de datos masivos que requieren procesado de datos en streaming sobre estructuras de datos basadas en grafos y árboles. En cualquier caso, partiendo de los requerimientos de nuestros casos de uso y usando herramientas que representan el estado del arte actual en programación genérica basada en patrones (centrándonos en los patrones dataflow y branch and bound), como objetivo general proponemos nueva tecnología que permita resolver, de manera transparente al programador, el problema de la planificación dinámica de la carga para arquitecturas heterogéneas, considerando que las soluciones deben ser portables en los distintos tipos de arquitecturas consideradas. La tecnología desarrollada se incorporará a lenguajes y librerías de paralelización orientadas a la productividad, algunos de las cuáles representan el estándar en programación genérica, lo que garantiza el impacto internacional de nuestra propuesta.

Ángeles Navarro

IP

Catedrática de Universidad en el Área de Arquitectura y Tecnología de Computadores de la UMA. Pertenece al grupo de investigación TIC-113, donde co-lidera junto al Dr. Rafael Asenjo Plaza el equipo de investigación "Parallel Programming Models and Compilers", formado por 6 doctores y 3 estudiantes de tesis. Tiene 25 publicaciones JCR, 50 contribuciones en conferencias internacionales y 7 capítulos de libro. Forma parte del Comité de Expertos de la Comisión Europea desde 2014, habiendo participado como evaluadora externa y monitora de proyectos en diversas convocatorias del FP7-ICT, H2020-FETHPC, H2020-ICT y H2020-SGA-LPMT. Tiene 2 patentes con examen previo concedido. Ha dirigido 7 tesis doctorales y está dirigiendo otras 2. Ha realizado 11 estancias de investigación en centros de referencia del área.

Rafael Asenjo

Co-IP

Catedrático de Universidad en el Área de Arquitectura y Tecnología de Computadores en la Universidad de Málaga y pertenece al grupo de investigación TIC-113. Co-lidera junto a la Dra. González Navarro el equipo "Parallel Programming Models and Compilers". Ha participado en 19 proyectos de investigación y dos contratos de investigación, publicado en 28 revistas internacionales indexadas en el JCR, 11 contribuciones en congresos "Core A" del IEEE y/o ACM (como ICS, PACT, IPDPS, ICPP y HiPC), 3 Keynotes por invitación, 5 Lecture Notes in Computer Science, 9 capítulos de libro, 39 congresos internacionales, participación en 18 comités de programa y 12 comités de organización de conferencias internacionales (General Chair, Registration Chair, etc), 15 conferencias por invitación, 21 congresos nacionales, impartido 6 tutoriales por invitación (PPoPP'18, SC'17, EuroPar'17 y PACT'04, entre ellos) y realizado 14 estancias de investigación en el extranjero (totalizando casi 3 años de estancias). Ha dirigido ocho tesis doctorales y está dirigiendo otras dos. Tiene 2 patentes con examen previo.

Invest.

Titular de Universidad en el Área de Arquitectura y Tecnología de Computadores de la Universidad de Málaga y pertenece al grupo de investigación TIC-113. Tiene 3 sexenios de investigación, 4 quinquenios docentes y 5 tramos del Complemento Autonómico Andaluz. Ha participado en 10 proyectos de investigación, publicado en 13 revistas internacionales indexadas en el JCR, 7 contribuciones a congresos CORE A del IEEE y/o ACM (como ICS, ICCS, IPDPS, ICPP y HiPC), 4 Lecture Notes in Computer Science, 3 capítulos de libro, 22 congresos internacionales, 8 congresos nacionales y realizado 1 estancia de investigación en el extranjero (4 meses). Ha codirigido una tesis doctoral.

Invest.

Titular de Universidad del Área de Arquitectura y Tecnología de Computadores de la Universidad de Málaga y pertenece al grupo de investigación TIC-113. Tiene 2 sexenios de investigación, 4 quinquenios docentes y 5 tramos del Complemento Autonómico Andaluz. Ha participado en 12 proyectos de investigación, publicado 13 artículos en revistas internacionales indexadas en el JCR, publicado 5 capítulos de libro y realizado 31 aportaciones en congresos internacionales y nacionales. Es autor de una patente de invención y un modelo de utilidad.

Eligius M. Hendrix

Invest.

Catedrático de Universidad en el Área de Arquitectura y Tecnología de Computadores en la Universidad de Málaga y pertenece al grupo de investigación TIC-146, Supercomputación y Algoritmos, uso de HPC en algoritmos de optimización. Tiene 75 publicaciones JCR y 84 publicaciones en congresos internacionales lo que resulta en 5 sexenios hasta 2018. Miembro del Editorial Board del Journal of Global Optimization desde 2002, evaluador de la ANEP y editor de 3 Special Issues del Journal of Global Optimization. Ha dirigido 10 tesis doctorales y 22 tesis de Master en el sistema de Bolonia. Es coautor de varios libros.

Colab.

Catedrático de Universidad en el Área de Arquitectura Tecnología de Computadores, Pertenece al grupo de investigación ARCOS (Arquitectura de Computadores, Comunicaciones y Sistemas) de la Universidad Carlos III de Madrid, dentro del cuál lidera la línea de investigación de "Modelos de Programación para la Mejora de Aplicaciones". Ha participado en un total de 22 proyectos de investigación (6 de ellos financiados por la Comisión Europea) y 19 contratos de investigación y transferencia de tecnología. Ha publicado 26 artículos en revistas JCR, 59 en congresos internacionales y 14 en congresos nacionales. También participa de forma habitual como revisor en los comités científicos de 9 revistas de ámbito internacional, habiendo participado como editor de números especiales en 3 de las mismas. Así mismo ha participado como miembro del comité de programa de más de 25 congresos de carácter internacional. Ha dirigido 4 tesis doctorales y dirige otras 3. Es miembro del comité internacional ISO/IEC JTC1/SC22/WG21 (Lenguaje C++), donde ha presentado más de 30 propuestas, muchas de las cuales se han incorporado a los estándares C++11, C++14, C++17 y C++20. Tiene 3 patentes.

Colab.

Titular de Universidad del área de Arquitectura de Tecnología de Computadores en la Universidad de Zaragoza y miembro del grupo de Arquitectura de Computadores y del Instituto de Investigación en Ingeniería de Aragón ambos de la misma institución. Entre 2012 y 2015 trabajó como Senior/Staff Engineer en Qualcomm Research Silicon Valley (QRSV), EE.UU. En QRSV fue arquitecto y responsable del interfaz energético del modelo de programación Qualcomm Symphony. Desde el año 2012, ha participado en 12 proyectos de investigación y ha publicado 15 artículos en revistas de ámbito internacional y 5 conferencias internacionales. Además firma 9 patentes internacionales en explotación y 4 solicitudes adicionales. Ha dirigido 1 tesis doctoral y 5 Trabajos Fin de Master. Acumula 5 contratos con empresas (2 regionales y 3 internacionales), incluyendo el contrato con Bigstream sobre procesado de streaming de datos.

Colab.

Profesor Contratado Doctor en el Departamento de Informática e Ingeniería de Sistemas de la Universidad de Zaragoza. Él y sus compañeros del Grupo de Arquitectura de Zaragoza (Gaz) pertenecen al Instituto de Investigación en Ingeniería de Aragón (I3A). Ha participado activamente en 5 Proyectos de Investigación nacionales (CICyT, TIN, PROTIN), en la publicación de 14 artículos de revistas internacionales, 10 artículos en congresos internacionales y 5 congresos nacionales. Así mismo, también realiza tareas de revisión para congresos y revistas internacionales. Ha dirigido 4 Trabajos Fin de Estudios y ha sido investigador principal de 1 proyecto de investigación.

Colab.

Reader en "Adaptive and Energy Efficient computing" en el Departamento de "Electronic Engineering", de la Universidad de Bristol, UK. Anteriormente fue Research Fellow en el Departamento de "Electronic Engineering at Loughborough University", UK, donde trabajó desde 1997 hasta 2004, alcanzando el grado de doctor en 2001 en una línea de arquitecturas hardware para compresión sin pérdidas a alta velocidad. En 2005 y 2006 trabajó en ST Microelectronics, Italia con una beca Marie Curie sobre procesadores reconfigurables para codificación de vídeo. En 2001 fue "Royal Society Fellow" en ARM, Cambridge, en modelado de potencia a nivel de sistema. Tiene 46 publicaciones en revistas internacionales y 84 en congresos internacionales. Ha participado en 14 proyectos de investigación, en 11 de los cuales como investigador principal. Tiene 3 patentes internacionales. Es "Fellow Member" de la "Royal Society Industry Fellows College", el "UK Higher Education Academy" y el "Engineering and Physical Research Reviewer College".

Colab.

Ingeniero Software en la empresa Shapelets, con domicilio fiscal en Málaga. Ha publicado en 4 revistas JCR y un congreso Core A, además de realizar estancias de investigación en UIUC-Illinois y un intership en la empresa Codeplay (Edimburgo) trabajando en el compilador de SYCL que dicha empresa desarrolla (SYCL es el lenguaje de programación usado en oneAPI DPC++). Actualmente es el principal desarrollador de Khiva que es la librería open-source para resolución de problemas de series temporales en CPU y GPU ofrecido por Shapelets.

Felipe Muñoz

Contratado

Estudiante de Tesis bajo la dirección de Ángeles Navarro y Rafael Asenjo y contratado unos meses con cargo al proyecto. Trabaja en el diseño de un algoritmo eficiente de la primitiva Matrix Profile.

Contratado

Estudiante de Máster bajo la dirección de Rafael Asenjo. Contratado con cargo al proyecto para la implementación y optimización de algoritmos de streaming masivos de datos con oneAPI en arquitecturas CPU+GPU.

+34 952 13 27 91

Complejo Tecnológico, Campus de Teatinos

29071, Málaga.

Spain

Built with Mobirise

Website Maker